アンプ切替リレー基板(入力側)

アンプを切り換える為のリレー基板で、アンプの入力(phono端子)を切り換えます。 8チャネルあります。リレーはG5V-2(OMRON)で設計しています。フォノ端子は2段1列の メーカ不詳のコネクタを使用しました。このコネクタはを入手出来ない時、あるいは 使用しない時の為にGNDランドを2つ設けてあります。 電源電圧は12Vを使用します。その為リレーも12Vになります。 この基板は金メッキレベラーで制作しました。生基板で販売しています。

- リレー:G5V-2-12V(OMRON)

- phono端子:2段1列品(メーカ不明,デジットにて購入)

- トランジスタアレイ:TD62063APG(東芝)

- 制御コネクタ:B10B-EH(JST)

- 基板サイズ:152.4x81.28mm(6000x3200mil),t1.6

回路は入力1ch(EHコネクタ2pin)、アンプへはphono出力8chになっています。 ただし、接続の仕方によっては例えば入力4ch、出力4chとした使い方も可能です。

リレーのON/OFFはトランジスタアレイ=TD62063によるオープンコレクタドライブです。 アンプのスピーカの切替えもリレーで行うと、スピーカのリレーを切り換えた後に フォノ端子側のリレーを切り換えます。このディレイはCRとダイオードで構成出来ます。 私はこれをテスト的にFPGAでディレイタイマーを構成してみました。 もちろんPIC等のCPUでも可能です。

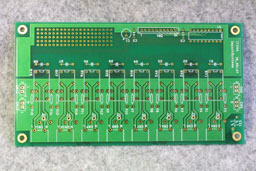

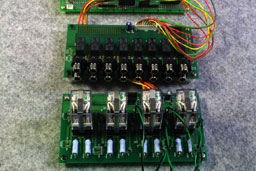

リレー基板部品面

phono端子は2段1列の物を8個使用します。基板は金メッキレベラー仕上げです。

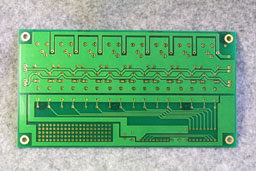

リレー基板半田面

phonoのGNDは左右共通でベタにしています。使用したコネクタは4pinでしたが1pinはフレームGNDでした。

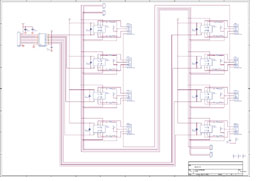

Base基板回路図

phonoの入力は基板左右にEHコネクタを設けています。片方は入力、もう一方は拡張に使います。

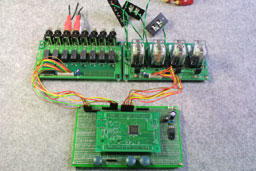

バラックでの実験の様子

手前の基板はFPGAによるディレイタイマーです。スピーカリレーが切り替わった後、約1秒後にフォノのリレーを切り換えます。

実装基板の拡大

リレー実装済みの2つの基板です。phono用のジャックはこういう物を使いました。